- Pengarang Lynn Donovan donovan@answers-technology.com.

- Public 2023-12-15 23:48.

- Terakhir diubah 2025-01-22 17:27.

VHDL dan Verilog dianggap sebagai bahasa desain digital untuk tujuan umum, sedangkan SystemVerilog mewakili versi yang disempurnakan dari Verilog . VHDL memiliki akar dalam Ada bahasa pemrograman baik dalam konsep maupun sintaks, sedangkan milik Verilog root dapat dilacak kembali ke HDL awal yang disebut Hilo dan bahasa pemrograman C.

Orang juga bertanya, mana yang lebih baik VHDL atau Verilog?

VHDL lebih bertele-tele daripada Verilog dan itu juga memiliki sintaks seperti non-C. Dengan VHDL , Anda memiliki peluang lebih tinggi untuk menulis lebih banyak baris kode. Verilog mempunyai sebuah lebih baik memahami pemodelan perangkat keras, tetapi memiliki tingkat konstruksi pemrograman yang lebih rendah. Verilog tidak bertele-tele seperti VHDL jadi itu sebabnya lebih kompak.

Juga, apa gunanya Verilog? Verilog adalah Bahasa Deskripsi Perangkat Keras; format tekstual untuk menggambarkan sirkuit dan sistem elektronik. Diterapkan pada desain elektronik, Verilog dimaksudkan untuk digunakan untuk verifikasi melalui simulasi, untuk analisis waktu, untuk analisis pengujian (analisis testabilitas dan penilaian kesalahan) dan untuk sintesis logika.

Dengan cara ini, apa perbedaan antara Verilog dan SystemVerilog?

utama perbedaan antara Verilog danSystemVerilog Apakah itu Verilog adalah Bahasa Deskripsi Perangkat Keras, sedangkan SistemVerilog adalah Deskripsi Perangkat Keras dan Bahasa Verifikasi Perangkat Keras berdasarkan Verilog . Secara singkat, SistemVerilog adalah versi yang disempurnakan dari Verilog dengan fitur tambahan.

Apa itu VHDL di VLSI?

VLSI Desain - VHDL Pendahuluan. Iklan. VHDL singkatan dari bahasa deskripsi perangkat keras sirkuit terintegrasi berkecepatan sangat tinggi. Ini adalah bahasa pemrograman yang digunakan untuk memodelkan sistem digital dengan aliran data, perilaku dan gaya pemodelan struktural.

Direkomendasikan:

Apa perbedaan antara Pebble Tec dan Pebble Sheen?

Pebble Tec terbuat dari kerikil alami yang dipoles yang menciptakan tekstur bergelombang dan permukaan tidak licin. Pebble Sheen menggabungkan teknologi yang sama dengan Pebble Tec, tetapi menggunakan kerikil yang lebih kecil untuk hasil akhir yang lebih licin

Apa perbedaan antara psikolog kognitif dan ahli saraf kognitif?

Psikologi kognitif lebih fokus pada pemrosesan informasi dan perilaku. Ilmu saraf kognitif mempelajari biologi yang mendasari pemrosesan informasi dan perilaku. ilmu saraf kognitif di pusat

Apa perbedaan antara merakit dan membongkar?

Adalah bahwa perakitan (komputasi) di microsoft net, blok bangunan aplikasi, mirip dengan dll, tetapi berisi kode yang dapat dieksekusi dan informasi yang biasanya ditemukan di perpustakaan tipe dll. Jenis informasi perpustakaan dalam perakitan, yang disebut manifes, menjelaskan fungsi publik, data, kelas, dan versi

Apa perbedaan antara kelas dalam dan kelas bersarang?

Kelas yang dideklarasikan tanpa menggunakan static disebut inner class atau non static nested class. Kelas statis bersarang adalah tingkat kelas seperti anggota statis lainnya dari kelas luar. Padahal, kelas dalam terikat dengan instance dan dapat mengakses anggota instance dari kelas terlampir

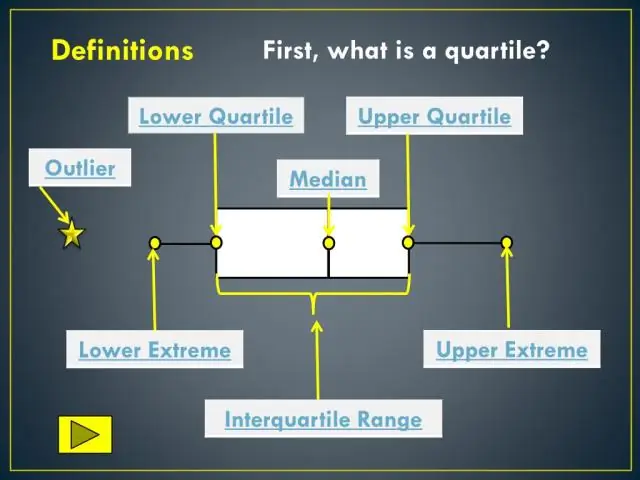

Apa perbedaan antara plot kotak dan kumis dan plot kotak?

Plot kotak dan kumis (kadang disebut plot kotak) adalah grafik yang menyajikan informasi dari ringkasan lima angka. Dalam plot kotak dan kumis: ujung-ujung kotak adalah kuartil atas dan bawah, jadi kotak itu mencakup rentang antarkuartil. median ditandai dengan garis vertikal di dalam kotak